Przegląd procesu półprzewodnikowego

Proces półprzewodnikowy obejmuje przede wszystkim zastosowanie technologii mikrofabrykacji i folii w celu pełnego połączenia chipów i innych elementów w różnych obszarach, takich jak podłoża i ramki. Ułatwia to wyciągnięcie końcówek przewodów i hermetyzację plastikowym środkiem izolacyjnym, tworząc zintegrowaną całość, przedstawioną jako trójwymiarowa struktura, ostatecznie kończąc proces pakowania półprzewodników. Pojęcie procesu półprzewodnikowego odnosi się także do wąskiej definicji pakowania chipów półprzewodnikowych. W szerszej perspektywie odnosi się do inżynierii opakowań, która polega na podłączeniu i zamocowaniu do podłoża, skonfigurowaniu odpowiedniego sprzętu elektronicznego i zbudowaniu kompletnego systemu o silnym kompleksowym działaniu.

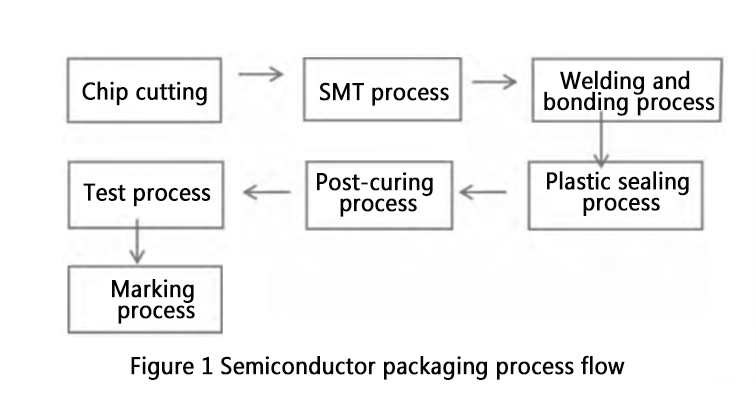

Przebieg procesu pakowania półprzewodników

Proces pakowania półprzewodników obejmuje wiele zadań, jak pokazano na rysunku 1. Każdy proces ma specyficzne wymagania i ściśle powiązane przepływy pracy, co wymaga szczegółowej analizy na etapie praktycznym. Konkretna treść jest następująca:

1. Cięcie wiórów

W procesie pakowania półprzewodników cięcie chipów polega na krojeniu płytek krzemowych na pojedyncze chipy i szybkim usuwaniu resztek krzemu, aby zapobiec zakłóceniom w późniejszej pracy i kontroli jakości.

2. Montaż chipów

Proces montażu chipa skupia się na uniknięciu uszkodzenia obwodu podczas szlifowania płytek poprzez nałożenie warstwy folii ochronnej, konsekwentnie podkreślając integralność obwodu.

3. Proces łączenia drutu

Kontrolowanie jakości procesu łączenia przewodów polega na użyciu różnych typów złotych przewodów do łączenia pól łączących chipa z polami ramy, zapewniając w ten sposób możliwość połączenia chipa z obwodami zewnętrznymi i zachowując ogólną integralność procesu. Zazwyczaj stosuje się druty ze złota domieszkowanego i druty ze złota stopowego.

Domieszkowane złote druty: typy obejmują GS, GW i TS, odpowiednie dla wysokiego łuku (GS: > 250 μm), średnio-wysokiego łuku (GW: 200-300 μm) i średnio-niskiego łuku (TS: 100-200 μm) wiązanie odpowiednio.

Druty ze złota stopowego: typy obejmują AG2 i AG3, odpowiednie do łączenia przy niskim łuku (70-100 μm).

Opcje średnic tych drutów wahają się od 0,013 mm do 0,070 mm. Wybór odpowiedniego typu i średnicy w oparciu o wymagania operacyjne i normy ma kluczowe znaczenie dla kontroli jakości.

4. Proces formowania

Główny obwód w elementach formierskich obejmuje hermetyzację. Kontrolowanie jakości procesu formowania zabezpiecza elementy, zwłaszcza przed działaniem sił zewnętrznych powodujących różnego stopnia uszkodzenia. Wiąże się to z dokładną analizą właściwości fizycznych komponentów.

Obecnie stosowane są trzy główne metody: opakowania ceramiczne, opakowania z tworzyw sztucznych i opakowania tradycyjne. Zarządzanie proporcjami każdego rodzaju opakowania ma kluczowe znaczenie, aby sprostać światowym wymaganiom w zakresie produkcji chipów. Podczas tego procesu wymagane są wszechstronne możliwości, takie jak wstępne podgrzewanie chipa i ramki prowadzącej przed kapsułkowaniem żywicą epoksydową, formowanie i utwardzanie po formie.

5. Proces utwardzania

Po procesie formowania wymagana jest obróbka po utwardzaniu, skupiająca się na usunięciu wszelkich nadmiarów materiałów wokół procesu lub opakowania. Kontrola jakości jest niezbędna, aby uniknąć wpływu na ogólną jakość i wygląd procesu.

6. Proces testowania

Po zakończeniu poprzednich procesów należy przetestować ogólną jakość procesu przy użyciu zaawansowanych technologii i urządzeń testujących. Ten krok obejmuje szczegółowe rejestrowanie danych, koncentrując się na tym, czy chip działa normalnie, w oparciu o jego poziom wydajności. Biorąc pod uwagę wysoki koszt sprzętu testującego, niezwykle ważne jest utrzymanie kontroli jakości na wszystkich etapach produkcji, w tym kontroli wizualnej i testów wydajności elektrycznej.

Testowanie wydajności elektrycznej: obejmuje testowanie obwodów scalonych przy użyciu automatycznego sprzętu testowego i upewnianie się, że każdy obwód jest prawidłowo podłączony do testów elektrycznych.

Kontrola wizualna: Technicy używają mikroskopów do dokładnej kontroli gotowych zapakowanych chipów, aby upewnić się, że są wolne od defektów i spełniają standardy jakości opakowań półprzewodników.

7. Proces znakowania

Proces znakowania polega na przeniesieniu przetestowanych chipów do magazynu półproduktów w celu końcowej obróbki, kontroli jakości, pakowania i wysyłki. Proces ten obejmuje trzy główne etapy:

1) Galwanizacja: Po uformowaniu doprowadzeń nakładany jest materiał antykorozyjny, aby zapobiec utlenianiu i korozji. Zwykle stosuje się technologię osadzania galwanicznego, ponieważ większość przewodów jest wykonana z cyny.

2) Gięcie: Następnie obrobione przewody są kształtowane, a pasek układu scalonego umieszczany jest w narzędziu do formowania przewodów, kontrolując kształt przewodów (typ J lub L) i pakowanie powierzchniowe.

3) Druk laserowy: Na koniec na uformowanych produktach drukowany jest wzór, który służy jako specjalny znak w procesie pakowania półprzewodników, jak pokazano na rysunku 3.

Wyzwania i rekomendacje

Badanie procesów pakowania półprzewodników rozpoczyna się od przeglądu technologii półprzewodników w celu zrozumienia jej zasad. Następnie zbadanie przebiegu procesu pakowania ma na celu zapewnienie skrupulatnej kontroli podczas operacji, przy wykorzystaniu udoskonalonego zarządzania w celu uniknięcia rutynowych problemów. W kontekście współczesnego rozwoju kluczowe znaczenie ma identyfikacja wyzwań w procesach pakowania półprzewodników. Zaleca się skupienie się na aspektach kontroli jakości, dokładne opanowanie kluczowych punktów, aby skutecznie poprawić jakość procesu.

Analizując z punktu widzenia kontroli jakości, podczas wdrażania występują znaczne wyzwania ze względu na liczne procesy o określonej treści i wymaganiach, z których każdy wpływa na siebie. Podczas operacji praktycznych konieczna jest ścisła kontrola. Przyjmując skrupulatne podejście do pracy i stosując zaawansowane technologie, można poprawić jakość procesu pakowania półprzewodników i poziom techniczny, zapewniając wszechstronną skuteczność aplikacji i osiągając doskonałe ogólne korzyści (jak pokazano na rysunku 3).

Czas publikacji: 22 maja 2024 r