Wafle krzemowo-na izolatorze (SOI) firmy Semicera przodują w innowacjach w zakresie półprzewodników, oferując lepszą izolację elektryczną i doskonałą wydajność cieplną. Struktura SOI, składająca się z cienkiej warstwy krzemu na podłożu izolacyjnym, zapewnia krytyczne korzyści dla wysokowydajnych urządzeń elektronicznych.

Nasze płytki SOI zostały zaprojektowane tak, aby minimalizować pojemność pasożytniczą i prądy upływowe, co jest niezbędne przy opracowywaniu układów scalonych o dużej prędkości i małej mocy. Ta zaawansowana technologia zapewnia wydajniejszą pracę urządzeń, większą prędkość i mniejsze zużycie energii, co jest kluczowe dla współczesnej elektroniki.

Zaawansowane procesy produkcyjne stosowane przez firmę Semicera gwarantują produkcję wafli SOI o doskonałej jednorodności i konsystencji. Jakość ta jest niezbędna w zastosowaniach w telekomunikacji, motoryzacji i elektronice użytkowej, gdzie wymagane są niezawodne i wydajne komponenty.

Oprócz korzyści elektrycznych, płytki SOI firmy Semicera zapewniają doskonałą izolację termiczną, poprawiając rozpraszanie ciepła i stabilność w urządzeniach o dużej gęstości i dużej mocy. Ta cecha jest szczególnie cenna w zastosowaniach, które wiążą się ze znacznym wytwarzaniem ciepła i wymagają efektywnego zarządzania ciepłem.

Wybierając wafel Silicon On Insulator firmy Semicera inwestujesz w produkt wspierający rozwój najnowocześniejszych technologii. Nasze zaangażowanie w jakość i innowacyjność gwarantuje, że nasze płytki SOI spełniają rygorystyczne wymagania dzisiejszego przemysłu półprzewodników, stanowiąc podstawę dla urządzeń elektronicznych nowej generacji.

| Rzeczy | Produkcja | Badania | Atrapa |

| Parametry kryształu | |||

| Polityp | 4H | ||

| Błąd orientacji powierzchni | <11-20 >4±0,15° | ||

| Parametry elektryczne | |||

| Domieszka | Azot typu n | ||

| Oporność | 0,015-0,025 oma·cm | ||

| Parametry mechaniczne | |||

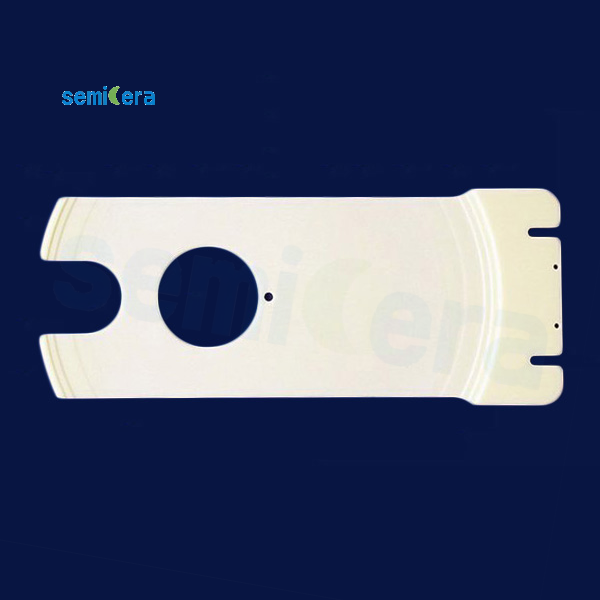

| Średnica | 150,0 ± 0,2 mm | ||

| Grubość | 350±25 μm | ||

| Podstawowa orientacja płaska | [1-100]±5° | ||

| Podstawowa długość płaska | 47,5 ± 1,5 mm | ||

| Mieszkanie wtórne | Nic | ||

| TTV | ≤5 µm | ≤10 µm | ≤15 μm |

| LTV | ≤3 μm (5 mm * 5 mm) | ≤5 μm (5mm*5mm) | ≤10 μm (5 mm * 5 mm) |

| Ukłon | -15μm ~ 15μm | -35μm ~ 35μm | -45μm ~ 45μm |

| Osnowa | ≤35 μm | ≤45 µm | ≤55 μm |

| Chropowatość przodu (Si-face) (AFM) | Ra≤0,2nm (5μm*5μm) | ||

| Struktura | |||

| Gęstość mikrorurek | <1 szt./cm2 | <10 szt./cm2 | <15 szt./cm2 |

| Zanieczyszczenia metaliczne | ≤5E10atomów/cm2 | NA | |

| BPD | ≤1500 szt./cm2 | ≤3000 szt./cm2 | NA |

| TSD | ≤500 szt./cm2 | ≤1000 szt./cm2 | NA |

| Jakość przodu | |||

| Przód | Si | ||

| Wykończenie powierzchni | Si-face CMP | ||

| Cząstki | ≤60ea/wafel (rozmiar ≥0,3μm) | NA | |

| Zadrapania | ≤5 szt./mm. Długość skumulowana ≤Średnica | Długość skumulowana ≤2*Średnica | NA |

| Skórka pomarańczowa/pestki/plamy/prążki/pęknięcia/zanieczyszczenia | Nic | NA | |

| Wióry/wcięcia/pęknięcia/płytki sześciokątne na krawędziach | Nic | ||

| Obszary politypowe | Nic | Powierzchnia skumulowana ≤20% | Powierzchnia skumulowana ≤30% |

| Znakowanie laserowe z przodu | Nic | ||

| Powrót Jakość | |||

| Wykończenie tyłu | CMP z twarzą C | ||

| Zadrapania | ≤5ea/mm, skumulowana długość ≤2*średnica | NA | |

| Wady grzbietu (odpryski/wcięcia krawędzi) | Nic | ||

| Szorstkość pleców | Ra≤0,2nm (5μm*5μm) | ||

| Tylne znakowanie laserowe | 1 mm (od górnej krawędzi) | ||

| Krawędź | |||

| Krawędź | Ścięcie | ||

| Opakowanie | |||

| Opakowanie | Epi-ready z opakowaniem próżniowym Opakowanie kasetowe składające się z wielu wafli | ||

| *Uwagi: „NA” oznacza brak żądania. Pozycje niewymienione mogą odnosić się do SEMI-STD. | |||